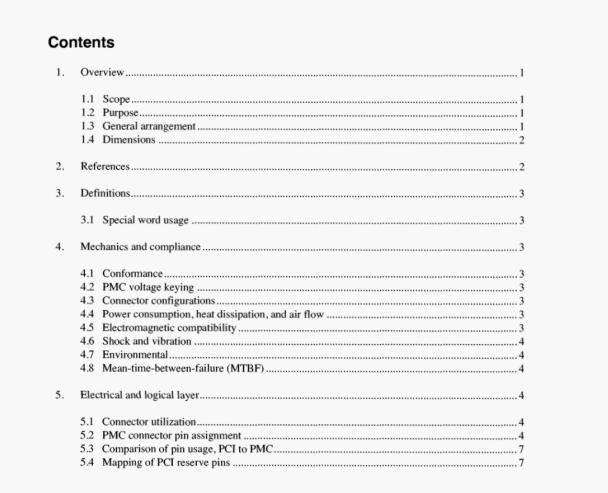

IEEE Std 1386.1:2001 pdf free download.IEEE Standard Physical and Environmental Layers for PCl Mezzanine Cards (PMC).

4.6 Shock and vibration

Each PMC vendor shall document in the product’s literature to which shock and vibration standards and towhat level(s) the product was designed and tested to (if tests were performed).

4.7 Environmental

Each PMC vendor shall document in the product ‘s literature to which environmental standards and to whatlevel(s) the product was designed and tested (if tests were performed).

4.8 Mean-time-between-failure (MTBF)

Each PMC vendor shall state in the product ‘s literature the calculated mean-time-between-failure (MTBF)for which environmental level, and state what method was used to calculate the MTBF number(s).

5. Electrical and logical layer

5.1 Connector utilization

The PMC and associated host connector pin assignments are based on specific signal integrity rules as wellas power distribution.The 5 V pins are assigned to Pn1/Jnl connector, the 3.3 V pins are assigned to Pn2/Jn2connector, and the V(IO) to Pn1/Jnl and Pn3/Jn3 connectors. All signal pins are adjacent to a voltage orground pin with the clock (CLK) pin surrounded by three ground pins.

The Pn1/Jn1 and Pn2/Jn2 connectors are always present and contain the signals for the 32-bit PCI Bus.When the PCI Bus is expanded to 64 bits, the Pn3/In3 connector is used for these signals.User defined lOsignals are assigned to the Pn4/Jn4 connector.The Pn3/Jn3 and Pn4/Jn4 connectors do not need to be presenton either the PCI mezzanine card (PMC) or the host when those signals are not used.Use of PCI bus reserve(PCI-RSVD) and PMC reserved (PMC-RSVD) pins are not allowed as their use may be defined by futureversions of the PCI specifications or by this standard, respectively.All Pn1/Jn1 and Pn2/Jn2 connector pinsare fixed and shall not be reassigned to other functions.

Note that the PCI signals are completely defined in PCI Local Bus Specification, Revision 2.2, 1998.

Pn4/Jn4 connectors are for user-defined L/O functions. The mapping of these IO signals to the backplane isdefined in IEEE Std 1386-2001 for Multibus applications.Mapping of I/O signals off the rear of VMEboards through VME backplanes is defined and controlled by the VME International Trade Association(VITA).4 Mapping of UO signals off the rear of CompactPCl boards through CompactPCl backplanes isdefined and controlled by the PCI Industrial Computer Manufacturers Group (PICMGR).

5.2 PMC connector pin assignment

PCI mezzanine cards and associated hosts that support PMC slots shall assign the local bus signal pins perthe pin assignment given in Table 1.

See Figure 2 and Figure 3 for connector orientation on the PMC and on the associated host, respectively.

IEEE Std 1386.1:2001 pdf free download