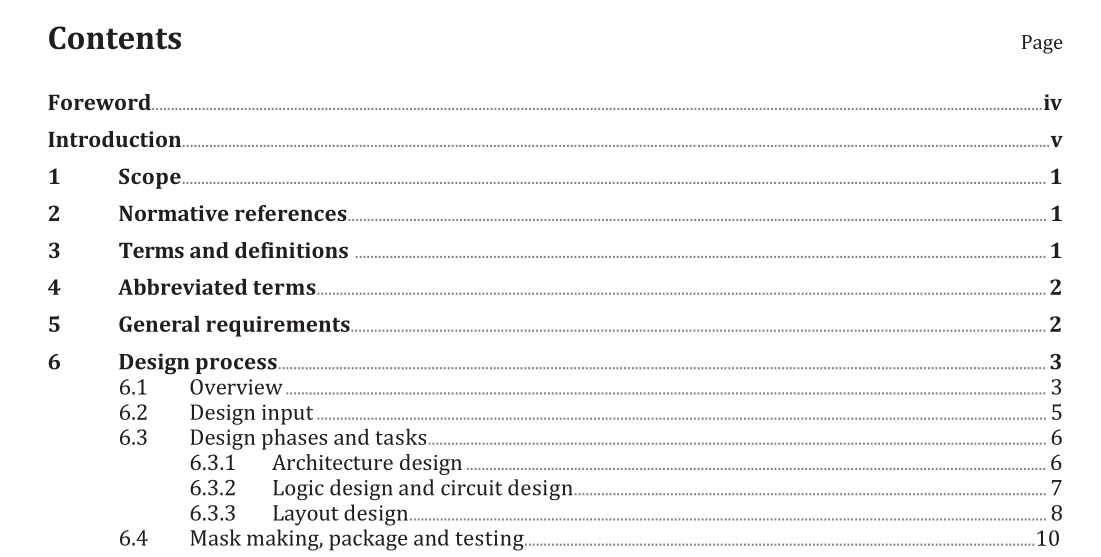

BS ISO 18257:2016 pdf download.Space systems — Semiconductor integrated circuits for space applications — Design requirements

1 Scope

This document specifies the basic design requirements for semiconductor ICs for space applications,including its design process, as well as required tasks and requirements of each stage. Requirements of specific circuit design are not included.

2 Normative references

The following documents are referred to in text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 61967-2, Integrated circuits — Measurement of electromagnetic emissions

IEC 62132, Integrated circuits — Measurement of electromagnetic immunity

IEC 62215-3:2013, Integrated circuits — Measurement of impulse immunity — Part 3: Non-synchronous transient injection method

IEEE 1149.1, IEEE standard for test access port and boundary — Scan architecture

3 Terms and definitions

For the purposes of this document, the terms defined in ISO 10795 and the following apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

— IEC Electropedia: available at http://www.electropedia.org/

— ISO Online browsing platform: available at http://www.iso.org/obp

3.1 programmable logic device

PLD

hardware-programmable device

EXAMPLE FPGA, CPLD, etc.

3.2 suitability

degree to which a product meets its requirements

3.3 environment adaptability

ability to achieve the entire product’s intended functions, performance and (or) capacity for protecting itself under various environments within its life cycle

3.4 testability

ability to perform function and performance testing of the circuit, position the failure of the circuit and select qualified circuit chip as soon as possible

6.3.2.1 Overview

In this stage, the high-level system design is transmitted and transformed to unit-level architecture description with the chosen technology library, and the input information of the next phase, such as layout constraints, placement and routing, and product testing and detailed pin description, etc. are generated. Logic design and circuit design are included. For digital circuits, verified gate-level netlist is generated; while for analogue circuit, verified transistor-level netlist is generated.

6.3.2.2 Design content

The following is the logic design and circuit design process.

a) Provide complete details of the circuit architecture.

b) Identify testability description and product testing methods, including extent of fault coverage.

c) Identify circuit and layout, which are considered together for simulation design.

d) Test concept of definition during design input and synthesis stage (i.e. scan path, testability logic,test points, test bus and boundary scan).

e) Identify radiation-hardened concept through design and synthesis stage, when applicable.

f) Implement step-by-step verification plans and verify the results obtained.

g) Validate pin leads and connection plans, paying special attention to technical constraints (i.e. power dissipation supply and pin definition).

h) Select buffers according to I/O requirements.

i) Ensure that output includes

1) updated datasheet (including output pin), and

BS ISO 18257:2016 pdf download